I3C dans les appareils mobiles

Pourquoi I3C est-il nécessaire ?

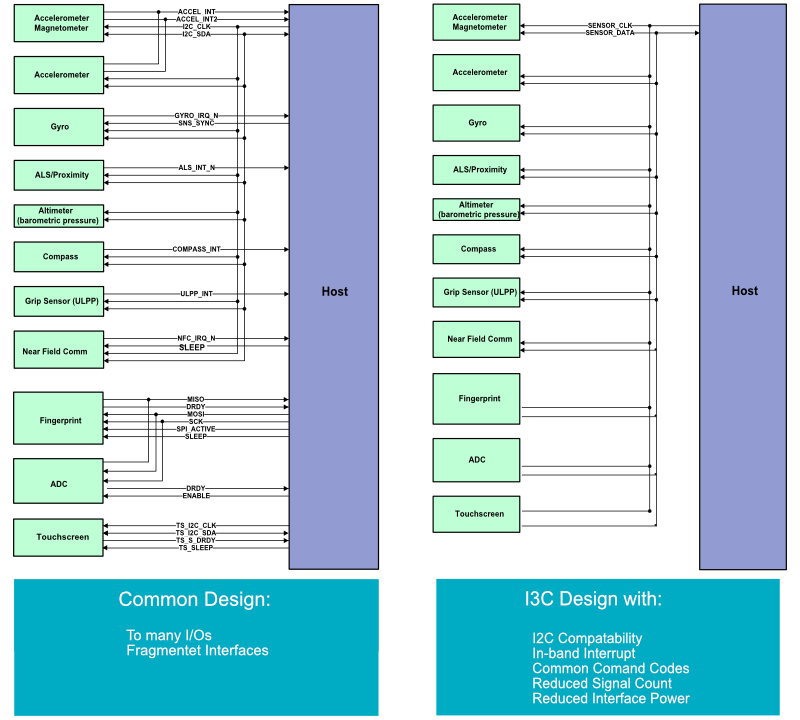

Les smartphones et autres appareils disposent d'un nombre rapidement croissant de capteurs mécaniques, de mouvements, biométriques et environnementaux, qui permettent une multitude de fonctions et de cas d'utilisation avec lesquels les entreprises différencient leurs produits. Cette prolifération de capteurs crée des défis de conception considérables, en particulier pour les développeurs de logiciels. Sans une méthode commune de connexion, chaque contrôleur hôte doit par exemple disposer de son propre logiciel système ou pilote pour prendre en charge ce matériel. Chaque implémentation de contrôleur hôte peut également fournir d'autres fonctions et optimisations.

Qu'est-ce que l'I3C et quels sont ses avantages pour les smartphones ?

I3C est une interface d'utilitaire et de bus de contrôle rapide et évolutive permettant de connecter des périphériques à un processeur d'application, d'optimiser l'intégration et d'améliorer la rentabilité. Il offre aux développeurs des possibilités sans précédent pour créer des designs innovants pour tout produit mobile - des smartphones aux wearables en passant par les systèmes dans les automobiles.

I3C permet de connecter des périphériques à un processeur d'application dans chaque appareil mobile et simplifie la connexion et la gestion de plusieurs capteurs dans un seul appareil. I3C est surtout destiné aux capteurs puissants. De plus, I3C transmet les interruptions sans lignes supplémentaires comme message dans le protocole. Avec 10,6 MBit/s, I3C dépasse I2C de plus de trois fois. Le mode High-Data-Rate atteint 33 MBit/s. Ainsi, dans certains cas, I3C peut remplacer la plus performante Serial Peripheral Interface (SPI). Les avantages de la spécification I3C sont la consommation d'énergie plus faible, le nombre réduit de broches ainsi que les chemins de single et la vitesse de transmission élevée tout en étant rétrocompatible avec I2C. De plus, les adresses des appareils peuvent être allouées de manière dynamique.

Touch over I3C est une option d'interface convergente pour les données tactiles traitées et brutes. CCI over I3C offre une latence plus rapide et plus faible et un contrôle plus efficace de la caméra.

Broches de signal I3C

I3C utilise les deux mêmes broches de signal que I²C, appelées SCL (horloge sérielle) et SDA (données sérielles). La principale différence est qu'ils fonctionnent comme I²C open-drain - sorties à tout moment, de sorte que sa vitesse est limitée par le temps de montée du signal lent résultant . I3C utilise le mode open-drain pour des raisons de compatibilité, mais passe aux sorties push-pull lorsque c'est possible et contient des modifications de protocole pour permettre cela plus souvent qu'en I²C. SCL est un signal d'horloge numérique traditionnel , qui est piloté pendant la transmission des données par le maître de flux de bus actuel avec une sortie push-pull. (Clock Stretching, une fonction I²C rarement utilisée, n'est pas supportée) Dans les transactions avec des appareils esclaves I²C, ce signal d'horloge a généralement un rapport cyclique d'environ 50%. Cependant, lors de la communication avec des esclaves I3C connus, le maître du bus peut passer à une fréquence plus élevée et / ou un changement de cycle de travail, de sorte que la période haute SCL est limitée à 40 ns au maximum. SDA transmet le flux de données série qui peut être piloté soit par le maître soit par l'esclave, mais à une fréquence déterminée par le signal SCL du maître.

Pour des raisons de compatibilité avec le protocole I²C, chaque transaction commence par le fait que SDA fonctionne comme une sortie à drain ouvert, ce qui limite la vitesse de transmission. Pour les messages adressés à un esclave I3C, le mode de pilotage SDA passe à push-pull après les premiers bits de la transaction, de sorte que la cadence peut encore être augmentée jusqu'à 12,5 MHz. Cette fonction à vitesse moyenne est appelée mode SDR (Standard Data Rate). En général, SDA est modifié immédiatement après le front descendant de SCL, et la valeur résultante est reçue au front montant suivant. Si le maître transmet SDA à l'esclave, cela se fait également sur le front descendant de SCL. Cependant, si l'esclave renvoie le contrôle de SDA au maître (par exemple après avoir confirmé son adresse avant une écriture), il libère SDA sur le front montant de SCL et le maître est responsable de maintenir la valeur reçue élevée pendant la durée de SCL. (Comme le maître contrôle SCL, le front montant est affiché en premier, il y a donc une courte période de chevauchement lorsque les deux contrôlent SDA. Mais comme les deux contrôlent la même valeur, il n'y a pas de conflit de bus)

Le cadrage I3C ?

Comme I²C, I3C utilise 9 cycles d'horloge pour envoyer chaque octet de 8 bits. Le 9ème cycle est cependant utilisé différemment. I²C utilise le dernier cycle pour une confirmation qui est envoyée à l'opposé des 8 premiers bits. I3C fonctionne de la même manière pour le premier octet (d'adresse) de chaque message et pour les messages compatibles I²C. Pour la communication avec les esclaves I3C, les octets de message après la première utilisation sont le 9e bit un bit de parité impair en écriture et un drapeau de fin -de données en lecture. Les écritures ne peuvent être terminées que par le maître. Le maître ou l'esclave peuvent terminer une lecture. L'esclave place SDA à un niveau bas pour indiquer qu'il n'y a plus de données disponibles. Le maître reprend alors SDA et génère un STOP ou un START répété. Pour qu'une lecture puisse continuer, l'esclave pousse SDA vers le haut pendant que SCL est bas avant le 9ème bit, mais laisse SDA flotter (Open-Drain) pendant que SCL est haut. Le maître peut à ce moment-là faire baisser SDA (une condition START répétée) pour interrompre le processus de lecture.

Neuvième bit I3C

Comme I²C, I3C utilise 9 cycles d'horloge pour envoyer chaque octet de 8 bits. Le 9ème cycle est cependant utilisé différemment. I²C utilise le dernier cycle pour une confirmation qui est envoyée en sens inverse des 8 premiers bits. I3C fonctionne de la même manière pour le premier octet (d'adresse) de chaque message et pour les messages compatibles I²C. Pour la communication avec les esclaves I3C, les octets de message après la première utilisation sont le 9e bit un bit de parité impair en écriture et un drapeau de fin -de données en lecture. Les écritures ne peuvent être terminées que par le maître. Le maître ou l'esclave peuvent terminer une lecture. L'esclave place SDA à un niveau bas pour indiquer qu'il n'y a plus de données disponibles. Le maître reprend alors SDA et génère un STOP ou un START répété. Pour qu'une lecture puisse continuer, l'esclave pousse SDA vers le haut pendant que SCL est bas avant le 9ème bit, mais laisse SDA flotter (Open-Drain) pendant que SCL est haut. Le maître peut à ce moment-là faire baisser SDA (une condition START répétée) pour interrompre le processus de lecture.

Arbitrage du bus I3C

Au début d'une trame, plusieurs appareils peuvent se disputer l'utilisation du bus, et le processus d'arbitrage du bus sert à choisir quel appareil recevra le contrôle de la ligne SDA. En I²C comme en I3C, l'arbitrage du bus avec la ligne SDA se fait en mode open drain, ce qui permet aux appareils qui transmettent un 0 binaire (bas) d'écraser les appareils qui transmettent un 1 binaire. Les appareils concurrents surveillent la ligne SDA pendant qu'ils fonctionnent en mode ouvert. Mode drain. Chaque fois qu'un appareil détecte un état haut (1 bit) en envoyant un état bas (0 bit) sur le SDA, il a perdu l'arbitrage et doit arrêter la compétition jusqu'à ce que la transaction suivante commence.

Chaque transaction commence par l'adresse de destination, et l'implémentation donne la priorité aux adresses de destination avec un numéro inférieur. La différence est que l'I²C n'a pas de limite à la durée de l'arbitrage (dans la situation rare mais légale de plusieurs appareils qui essaient d'envoyer un message au même appareil, le conflit n'est détecté qu'après l'octet d'adresse). Cependant, I3C garantit que l'arbitrage se termine au plus tard à la fin du premier octet. Ainsi, les pilotes push-pull et les cadences plus rapides peuvent être utilisés la plupart du temps. Cela se fait de différentes manières : I3C supporte plusieurs maîtres, mais ceux-ci ne sont pas symétriques. L'un d'entre eux est le maître actuel et est responsable de la génération de l'horloge.

Les autres appareils qui envoient un message sur le bus (interruptions dans la bande ou maîtres secondaires qui veulent utiliser le bus) doivent décider avant d'envoyer d'autres données en utilisant leur propre adresse. Ainsi, deux messages de bus légaux ne partagent pas le même premier octet, sauf si le maître et un autre appareil communiquent en même temps. I3C, comme I²C, permet plusieurs messages par transaction, séparés par des symboles "START répétés". L'arbitrage se fait par transaction, de sorte que ces messages successifs ne sont jamais soumis à un arbitrage. La plupart des transactions maîtres I3C commencent à l'adresse réservée 0x7E (1111110 2 ).

Comme cela a une priorité plus basse que n'importe quel appareil I3C, le maître sait, après avoir réussi l'arbitrage, qu'aucun autre appareil ne se bat pour le bus. Si des adresses basses sont attribuées aux appareils I3C comme cas particulier (I3C supporte l'attribution dynamique d'adresses contrôlée par le maître), 0x7E le maître connaît cet arbitrage , dès que l'adresse a gagné un arbitrage pour suffisamment de bits de tête pour la distinguer d'une adresse attribuée est terminé et il est possible de passer en mode push-pull sur SDA. Si toutes les adresses attribuées sont inférieures à 0x40 , cela se produit après le premier bit. Si toutes les adresses sont inférieures à 0x60 , cela se produit après le deuxième bit et ainsi de suite.

Dans le cas décrit ci-dessus, où le maître actuel commence une transaction avec l'adresse d'un appareil qui se bat lui-même pour utiliser le bus, les deux transmettent leurs octets d'adresse avec succès. Cependant, chacun s'attend à ce que l'autre confirme l'adresse (en tirant SDA bas) pour le bit de confirmation suivant. Par conséquent, aucun des deux ne remarquera le manque de reconnaissance. Dans ce cas, le message n'est pas envoyé, mais le maître gagne l'arbitrage : il est possible qu'un départ répété soit envoyé, suivi d'une nouvelle tentative qui sera réussie.

Codes de commande généraux

Une opération d'écriture 0x7E adressée à l'adresse réservée est utilisée pour effectuer une série d'opérations spéciales dans I3C. Tous les appareils I3C doivent recevoir et interpréter des processus d'écriture à cette adresse en plus de leurs adresses individuelles. Tout d'abord, une opération d'écriture composée uniquement de l'octet d'adresse et d'aucun octet de données n'a aucun effet sur les esclaves I3C, mais peut être utilisée pour simplifier l'arbitrage I3C. Comme décrit ci-dessus, ce préfixe peut accélérer l'arbitrage (si le maître supporte l'optimisation de la commutation sur les mid-bytes push-pull), et il simplifie le maître en évitant un cas d'arbitrage un peu délicat. Si l'écriture est suivie d'un octet de données, l'octet encode un "code d'instruction général", une opération I3C standardisée. Les codes d'instruction 0-0x7F sont des instructions de diffusion qui s'adressent à tous les esclaves I3C.

Ils peuvent être suivis de paramètres supplémentaires spécifiques à la commande. Les codes de commande 0x80-0xFE sont des commandes directes qui s'adressent à des esclaves individuels. Elles sont suivies d'une série de STARTs répétés et de l'écriture ou de la lecture dans certains esclaves. Pendant qu'une commande directe est exécutée, les opérations d'écriture ou de lecture par esclave transmettent des paramètres spécifiques à la commande. Cette opération remplace la réponse normale de l'esclave à un message I3C. Une commande directe peut être suivie de plusieurs messages par esclave, chacun étant précédé d'un START répété. Ce mode spécial se termine à la fin de la transaction (symbole STOP) ou au prochain message adressé à 0x7E . Certains codes de commande existent à la fois sous forme de diffusion et sous forme directe. Par exemple, les commandes pour activer ou désactiver les interruptions dans la bande peuvent être envoyées à des esclaves individuels ou envoyées à tous. Les commandes pour récupérer des paramètres d'un esclave (par exemple la commande GETHDRCAP pour demander à un appareil quels modes sont pris en charge avec un débit de données élevé) n'existent que sous forme directe.

Options HDR (High Data Rate)

Chaque transaction de bus I3C commence en mode SDR, mais le maître I3C peut émettre une commande de diffusion CCC "Enter HDR" qui informe tous les esclaves I3C que la transaction se poursuit dans un mode HDR spécifique. Les esclaves I3C qui ne supportent pas HDR peuvent alors ignorer le trafic du bus jusqu'à ce qu'ils voient une certaine séquence "HDR-Exit" qui les informe qu'il est temps d'écouter à nouveau le bus. (Le maître sait quels esclaves supportent HDR et n'essaiera donc jamais d'utiliser HDR pour communiquer avec un esclave qui ne le supporte pas) Certains modes HDR sont également compatibles avec les appareils I²C si les appareils I²C disposent d'un filtre de pointe de 50 ns dans la ligne SCL. Cela signifie qu'ils ignorent un niveau élevé sur la ligne SCL qui dure moins de 50 ns. Ceci est requis dans la spécification I²C, mais n'est pas implémenté de manière universelle, et toutes les implémentations n'ignorent pas les pics fréquemment répétés.

Il faut donc vérifier la compatibilité I3C-HDR. Les modes HDR compatibles utilisent des impulsions SCL de 45 ns maximum, de sorte que les appareils I²C les ignorent. Le mode HDR-DDR utilise une signalisation à double débit de données avec une horloge de 12,5 MHz pour atteindre un débit de données brutes de 25 Mbit / s (effectivement 20 Mbit / s). Cela nécessite de changer la ligne SDA pendant que SCK est élevé, une violation du protocole I²C, mais les appareils I²C ne voient pas la courte impulsion élevée sur SCL et ne remarquent donc pas la violation. Les modes HDR-TSP et HDR-TSL utilisent un des trois symboles comme chiffres ternaires (trits) :

Une transition de SDA et SCL (reçue dans les 12,8 ns l'une de l'autre), Une seule transition de SCL ou Une seule transition de SDA. Deux octets plus deux bits de parité (18 bits au total) sont divisés en six triplets de 3 bits, et chaque triplet est codé comme deux trits. À une vitesse de 25 Mtrit / s, un débit effectif de 33,3 Mbit / s est atteint. La paire de trits, qui se compose uniquement de deux transitions de SDA, n'est pas utilisée pour coder des données, mais pour encadrer, pour marquer la fin d'une séquence HDR. Bien que cela limite le temps maximum entre les transitions SCL à trois temps Trit, cela dépasse la limite de 50 ns pour les anciens appareils I²C. Par conséquent, le mode HDR-TSP (symbole ternaire, pur) ne peut être utilisé que sur un bus sans anciens appareils I²C. Pour autoriser les bus avec des appareils I²C (avec un filtre de pointe), il faut utiliser le mode HDR-TSL (symbole ternaire, héritage). Cela permet de conserver la compatibilité I²C grâce au Trit-Stuffing : si après un front montant au SCL, le Trit suivant n'est pas 0, l'émetteur insère un Trit de 1 (uniquement transition au SCL) et le récepteur l'ignore. Cela garantit que le SCL n'est jamais élevé plus d'un temps de Trit.

Classes d'appareils

Sur un bus I3C en mode standard (SDR), quatre classes d'appareils différentes peuvent être prises en charge :

- I3C maître principal

- I3C maître secondaire

- Esclave I3C

- Esclave I²C (anciens appareils).

Les fonctions I²C suivantes ne sont pas supportées dans I3C

Les résistances pull-up sont fournies par le maître I3C. Les résistances pull-up externes ne sont plus nécessaires. Clock Stretching - On attend des appareils qu'ils soient suffisamment rapides pour fonctionner à la vitesse du bus. Le maître I3C est la seule source d'horloge. Adresses I²C étendues (10 bits). Tous les appareils sur un bus I3C sont adressés avec une adresse de 7 bits. Les appareils I3C natifs ont une adresse unique de 48 bits, qui n'est utilisée que pour les attributions d'adresses dynamiques.

I3C Interface du contrôleur hôte

I3C HCI définit un ensemble commun de fonctions pour le contrôleur hôte et l'interface logicielle, ce qui permet de créer des définitions de classes basées sur un ensemble commun de fonctions. La définition permet des extensions et des optimisations spécifiques au fabricant afin d'intégrer plus facilement des fonctions à valeur ajoutée pour les smartphones, les wearables, l'Internet des objets (IoT) et les automobiles, et plus encore. La spécification offre au logiciel de la plate-forme un moyen efficace de communiquer avec les fonctions de l'appareil maître sur le bus I3C, et assure un fonctionnement à faible consommation d'énergie du contrôleur hôte. Résultat final : les développeurs ont le temps de se concentrer sur l'intégration de la caméra, du tactile et d'autres composants et fonctions pour différencier leurs produits. "

I3C Touch et Camera

I3C contient de nombreuses spécifications spécialement conçues pour l'industrie mobile. Ces extensions de spécifications pour des cas d'application spécifiques vont, par exemple, du tactile aux connexions de caméras et permettent aux développeurs de faciliter l'implémentation et d'économiser des coûts de développement.

I3C HCI, est également inclus dans la famille de spécifications I3C Touch, de sorte que les commandes tactiles et les flux de données multiples peuvent être utilisés pour ajouter des fonctions tactiles différenciées à un design. Les entreprises de traitement d'applications peuvent utiliser la spécification pour standardiser la méthode HCI utilisée dans leurs appareils. La spécification définit plusieurs optimisations basées sur l'utilisation typique. Par exemple, la fonction de commande combinée permet de transférer efficacement et une seule fois des transferts d'écriture puis de lecture sur le bus. Un autre exemple est la commande automatique qui permet de lire efficacement un grand tampon de données dans le contexte d'interruptions dans la bande.

Analyseur de protocole I3C et adaptateur hôte

PGY-I3C-EX-PD est l'outil leader qui permet aux concepteurs et aux ingénieurs de test de tester les constructions I3C par rapport à leurs spécifications, en configurant PGY-I3C-EX-ED comme maître / esclave, en générant le trafic I3C avec une fonction d'injection d'erreurs et en décodant les paquets de décodage de protocole I3C.