Description

L'analyseur logique PGY-LA-EMBD est le premier analyseur logique de l'industrie qui permet de dépanner les problèmes de timing et d'analyser simultanément les protocoles I2C, SPI, UART, I3C, SPMI, CAN/CAN FD et RFFE dans les conceptions embarquées. Tu peux ainsi résoudre rapidement les problèmes au niveau du circuit et du système. Cela permet de déboguer rapidement les problèmes au niveau du circuit et du système.

Le PGY-LA-EMBD offre une acquisition de données asynchrone à 1GS/seconde (timing) et une acquisition de données synchrone à 100MHz (état), ce qui en fait un outil de débogage idéal pour la résolution des problèmes de conception numérique. Les développeurs peuvent désormais analyser rapidement, en plus des problèmes de protocole, les problèmes de configuration et de temps de maintien, les glitches et les activités de données synchrones.

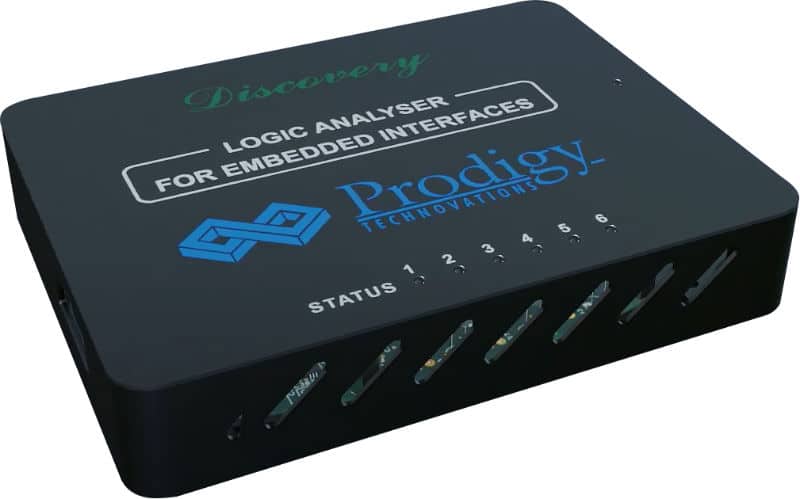

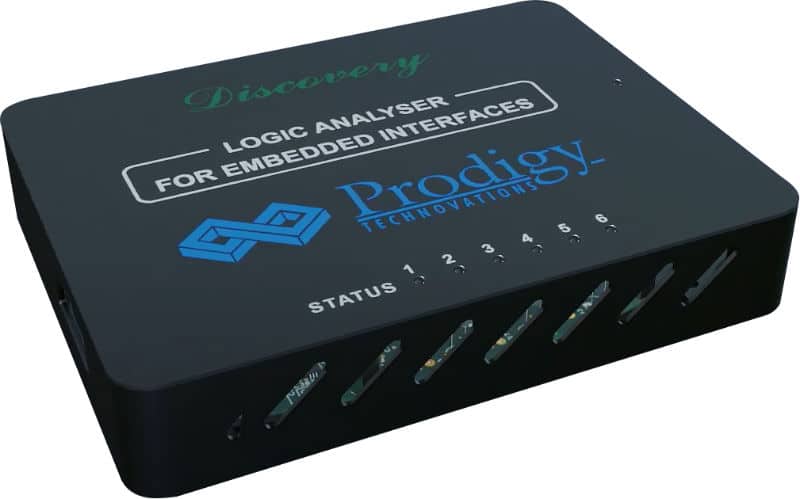

L'analyseur logique est un analyseur logique basé sur PC, conçu pour les professionnels exigeants. L'analyseur logique Discovery est idéal pour le dépannage des systèmes embarqués. L'analyseur logique a un facteur de forme très petit, de sorte qu'il peut être utilisé pour le dépannage lors d'une utilisation mobile. Les fonctions de décodage de protocole sont conçues pour le dépannage des problèmes de logique et de protocole des équipes de conception embarquées dans les domaines des biens de consommation, de l'industrie, de la domotique, de la santé et de l'éducation.

Les concepteurs de systèmes embarqués doivent collecter et traiter les données de plusieurs interfaces comme 2C, SPI, UART, I3C, SPMI, CAN/CAN FD et RFFE afin de développer une carte embarquée performante. Le PGY-LA-EMBD décode les bus et affiche l'activité du protocole avec des informations d'horodatage. C'est pourquoi c'est un outil idéal pour déboguer les problèmes d'intégration de matériel et de logiciel embarqué et pour optimiser les performances du logiciel.

Plusieurs marqueurs permettent de réaliser des mesures delta innovantes, essentielles pour les développeurs. La fonction de zoom permet à l'utilisateur d'observer certaines zones du signal.

Caractéristiques Analyseur de logique

- 16 canaux avec fonction d'analyse de protocole et de logique.

- 1GS/sec. Analyse du timing (asynchrone)

- analyse d'état à 100 MHz (synchrone)

- Analyse simultanée des protocoles I2C-SPI-UART-I3C-SPMI, CAN/CAN FD, et RFFE.

- Fonctions de déclenchement détaillées : Auto, modèle, reconnaissance de protocole (I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE) et timing (largeur d'impulsion et déclencheur de retard).

- Streaming intelligent des données du protocole. Analyseur à l'ordinateur hôte pour un enregistrement à long terme via l'interface USB3.0.

- Interface utilisateur graphique innovante et facile à utiliser.

- Analyse des erreurs du paquet de protocoles

- Offre des vues du timing, de la forme d'onde, de la liste et du protocole

- Fonction de filtre détaillée pour les données décodées par le protocole

- Format de rapport PDF et CSV.

- Support de l'API.

Une configuration simple

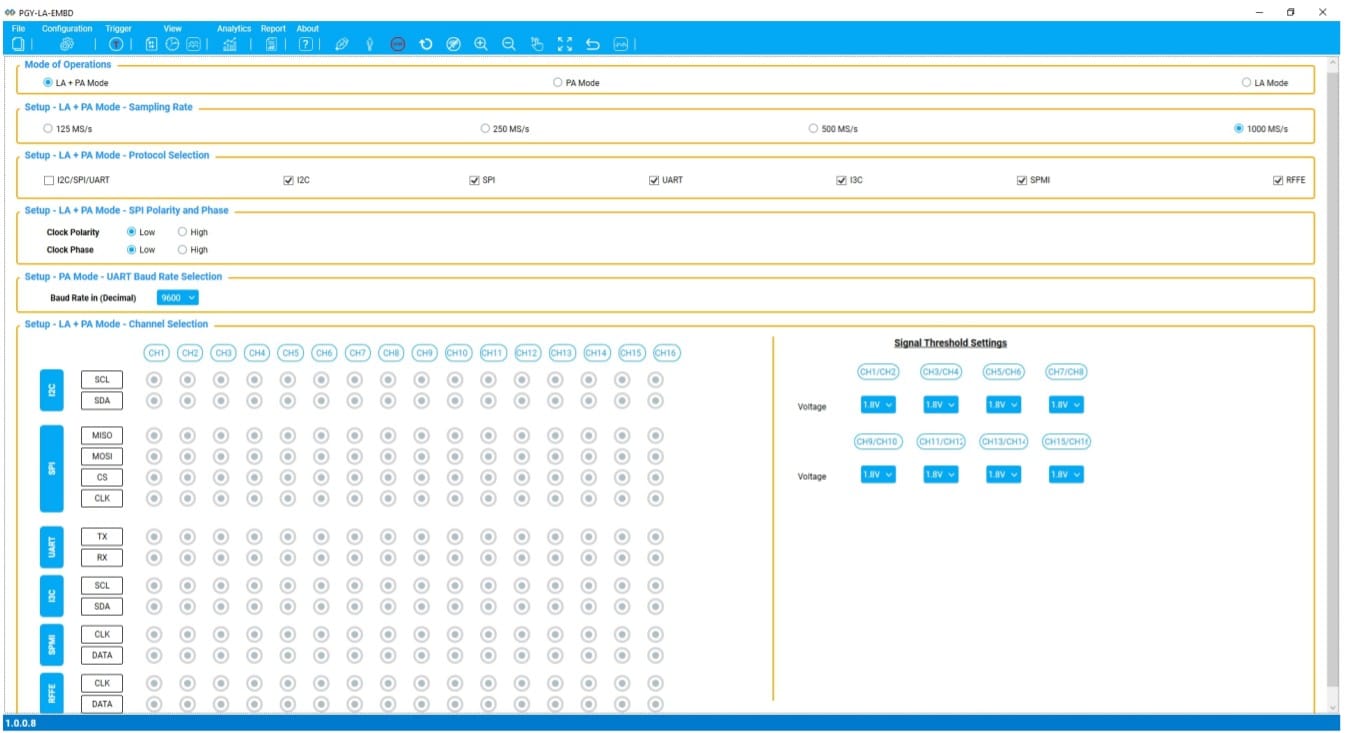

Les utilisateurs peuvent facilement configurer l'analyseur logique pour les interfaces embarquées en sélectionnant soit le mode d'analyse logique (LA), soit le mode d'analyse de protocole (PA), soit un mode combiné (LA+PA). Cela permet de configurer rapidement et facilement le produit et d'examiner les problèmes complexes au niveau du système soit dans l'analyse logique (analyse d'état, analyse temporelle), soit dans le décodage du protocole, soit les deux. La fonction de sauvegarde et de récupération garantit que les développeurs peuvent récupérer leurs détails de configuration personnalisés.

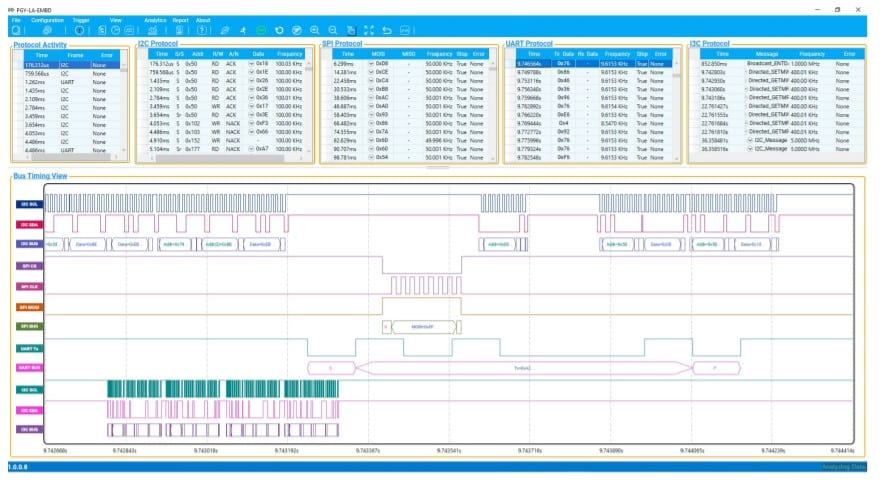

Plusieurs vues de domaine offrent la vue complète nécessaire sur l'état, le timing et l'activité de protocole de toutes les interfaces supportées. Les utilisateurs peuvent facilement configurer l'analyseur pour qu'il affiche les vues de timing, de logique et de décodage de protocole afin de permettre un aperçu facile de la conception. le menu de configuration permet de définir différentes conditions de déclenchement afin d'enregistrer l'activité du timing et du protocole lors d'événements spécifiques. Les résultats décodés peuvent être affichés dans la fenêtre de liste de timing, de logique et de protocole avec autocorrélation. Cette vue complète des informations en fait l'un des meilleurs du secteur et offre une solution conviviale pour déboguer l'activité de protocole des interfaces embarquées et pour analyser les problèmes de timing. Plusieurs curseurs aident les développeurs à examiner les détails de leur performance de conception.

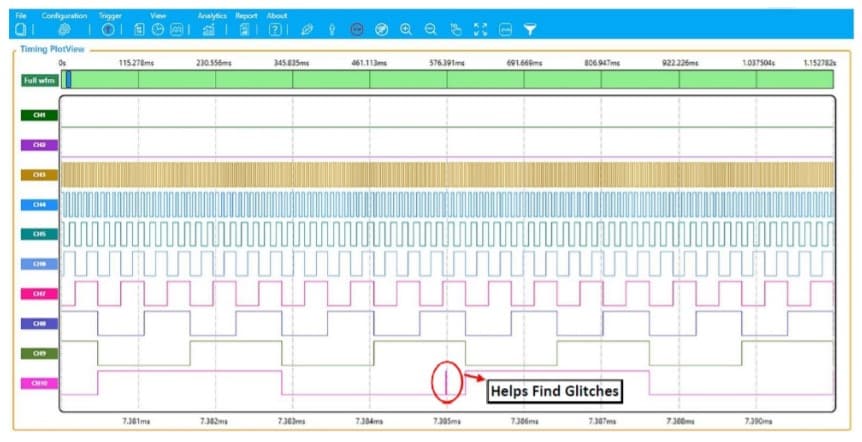

Vue du timing

L'affichage du timing est une fonction unique du PGY-LA-EMBD qui permet aux développeurs d'obtenir une vue détaillée des informations de timing de leurs signaux. L'affichage du timing utilise un signal d'horloge interne pour représenter la forme d'onde. La sélection flexible du taux d'échantillonnage permet aux développeurs d'examiner les glitches qui peuvent causer des problèmes dans le fonctionnement de leurs designs. La fonction de regroupement permet aux développeurs de regrouper différents signaux apparentés pour une meilleure visualisation et analyse. Les fonctions de marquage et de zoom facilitent l'analyse des erreurs de timing. La possibilité d'analyser n'importe quel point de l'ensemble de données capturé garantit une recherche et une analyse faciles des erreurs sur une longue période de capture.

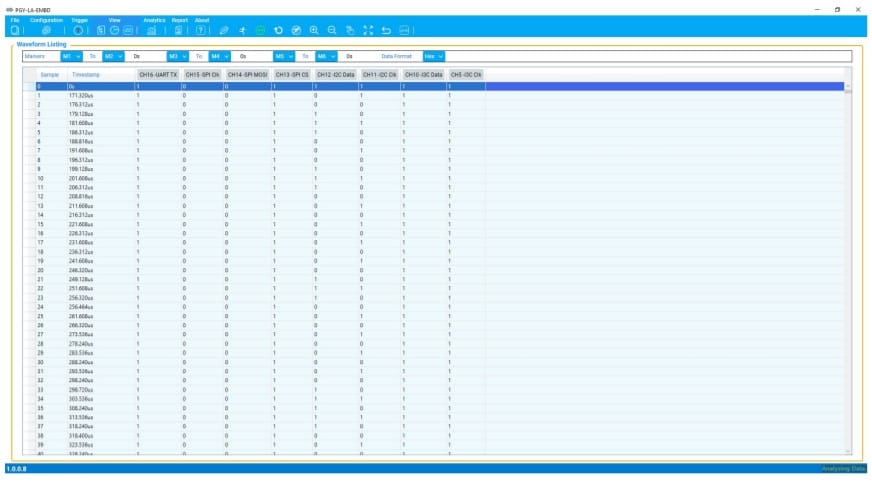

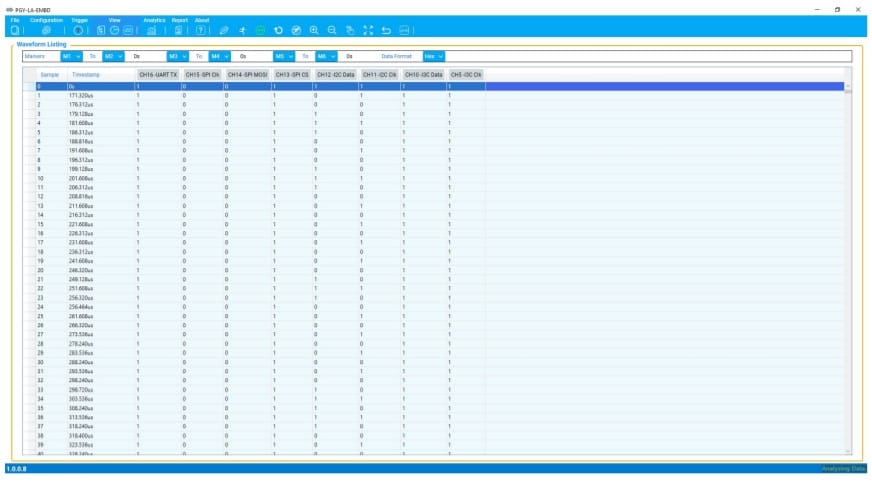

Vue de l'état/vue du listing de la forme d'onde

Vue de décodage de protocole

La fenêtre Protocol Activity montre les informations de paquet décodées dans chaque état et tous les détails de paquet avec les informations d'erreur dans les paquets. Cela permet aux équipes de développement d'avoir un aperçu au niveau du système. Les différentes fenêtres de décodage de protocole sont basées sur les interfaces sélectionnées et garantissent un affichage simple pour les équipes de développement. La trame sélectionnée dans la fenêtre de listage des protocoles est autocorrélée dans l'affichage du timing afin d'afficher les informations de timing du paquet. Les erreurs de protocole sont mises en évidence afin de garantir que les développeurs les remarquent facilement.

De puissantes fonctions de déclenchement

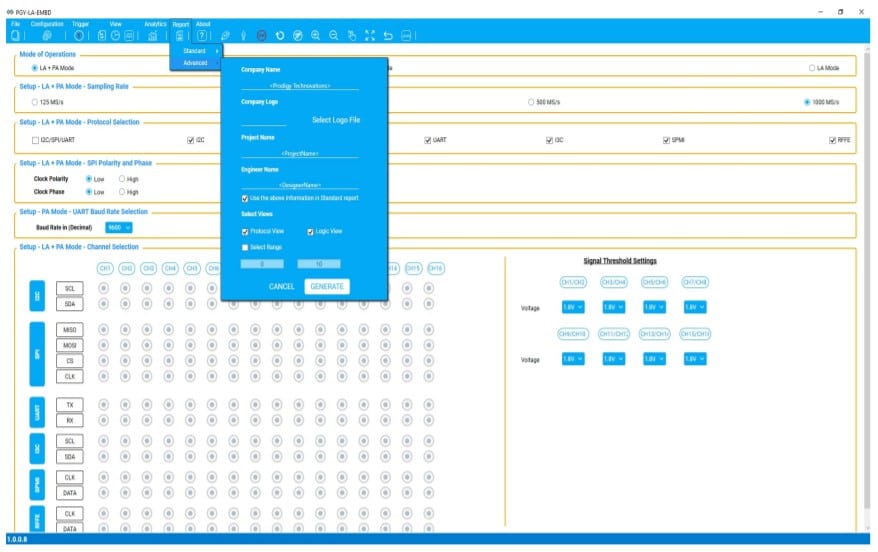

Rapport

Le rapport peut être créé au format PDF ou CSV avec toutes les informations sur les signaux, les tracés et les détails personnalisés tels que le nom de l'entreprise, le logo, le nom du testeur, la date et l'heure, afin de garantir que les concepteurs puissent documenter tous les détails et partager le rapport.

Garantie

Le matériel et les logiciels sont couverts par une garantie d'un an. Les sondes sont couvertes par une garantie de trois mois pour tous les défauts de fabrication

Spécifications techniques

| Spécification |  |

|---|---|

| Nombre de canaux | 16 canaux logiques |

| Vitesse d'état | 1GS/s (détection asynchrone) |

| Vitesse de synchronisation | Souder des sondes actives |

| Nombre de soutien State-Clock | Deuxièmement, flexibilité pour le balayage sur le front montant ou descendant |

| Longueur du jeu de données | Streaming continu intelligent des données sur le HDD/SSD de l'ordinateur hôte |

| Support du niveau de tension | 0 à 5 V avec flexibilité pour définir le seuil logique |

| Diagramme de forme d'onde | Affiche les formes d'ondes avec un diagramme de bus configurable de manière flexible |

| Vue de liste | Répertorie tous les échantillons de données à chaque point d'échantillonnage |

| Déclencheurs pour LA | Déclencheur de motif, déclencheur de largeur d'impulsion, déclencheur de délai |

| Support de décodage de protocole | I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE |

| Décodage simultané de I2C, SPI, UART | Oui, connecte le bus I2C, SPI et UART à l'analyseur logique. Capture simultanément les données du bus et les affiche Vue corrélée au temps avec les formes d'onde de temps correspondantes. |

| Vue du protocole avec vue du timing (PA+LA) | Affiche simultanément les données décodées par le protocole avec un taux d'échantillonnage élevé et une forme d'onde de synchronisation |

| Soutien API | Soutien pour l'automatisation du fonctionnement avec Python et C++ |

| Type de connexion | Flying Lead Probe avec prises #16 Micro Grabber Test Clips comme accessoire optionnel |

| Déclencheurs externes | Connecteur SMA Trigger-Out |

| Marqueurs | Six, avec des informations delta entre deux repères. |

| Appels | Vue du timing Vue de l'état/de la logique/de la liste des signaux Vue du protocole Diagramme de bus pour afficher les paquets de protocole avec le diagramme du timing Plot Auto Trigger - Default (Trigger on any Paket) |

| Déclencheur de protocole | Déclencheur de modèle Déclencheur conscient du protocole- UART : bit de départ, bit de parité, données SPI : données MOSI, données MISO I2C : bit START, adresse, données, adresse plus données, ACK, NACK, START répété, bit STOP Déclencheur de paramètre de timing : largeur d'impulsion (positive ou négative) Déclencheur de délai. |

| Durée d'acquisition | Streaming intelligent des données de protocole pour héberger le HDD/SSD. |

| Rapport | Création de rapports au format PDF et CSV |

| Connectivité hôte | USB 3.0 type-C |

| Dimensions | 115 mm x 90 mm x 25 mm |

| Poids | 300 g |

.jpg)

.jpg)

.jpg)

.jpg)