Interface sérielle périphérique améliorée (eSPI)

Le leader du secteur Intel définit la nouvelle norme eSPI comme Amélioration des transactions de données avec une consommation d'énergie et des coûts réduits. Les fabricants peuvent facilement l'intégrer dans leurs produits - au niveau de la puce, de la carte et du système.

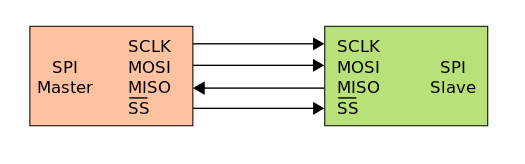

Base SPI

Les appareils SPI communiquent en mode duplex intégral en utilisant une architecture maître-esclave (terminologie alternative comme langage principal et secondaire) avec un seul maître. L'appareil maître crée la trame pour la lecture et l'écriture. Plusieurs appareils esclaves sont pris en charge en sélectionnant des lignes de sélection d'esclave (SS) individuelles, parfois appelées lignes de sélection de puce (CS).

Fonctions

Au total, les fonctions comprennent une interface à quatre fils (réception, envoi, sélection de l'horloge et de l'esclave) et trois configurations :

- IO unique (ou IO standard) : Horloge, sélection de puce, signal de données unidirectionnel (MOSI), signal de données unidirectionnel (MISO)

- DUAL IO : horloge, sélection de puce, signal de données bidirectionnel (IO0), signal de données bidirectionnel (IO1)

- QUAD IO : Horloge, sélection de puce, signal de données bidirectionnelles (IO0), signal de données bidirectionnelles (IO1), signal de données bidirectionnelles (IO0=2), signal de données bidirectionnelles (IO3)

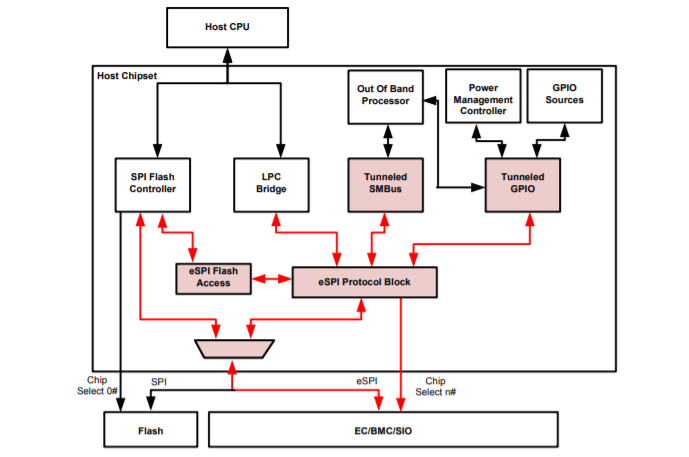

eSPI : quels sont les avantages par rapport aux autres systèmes de bus ?

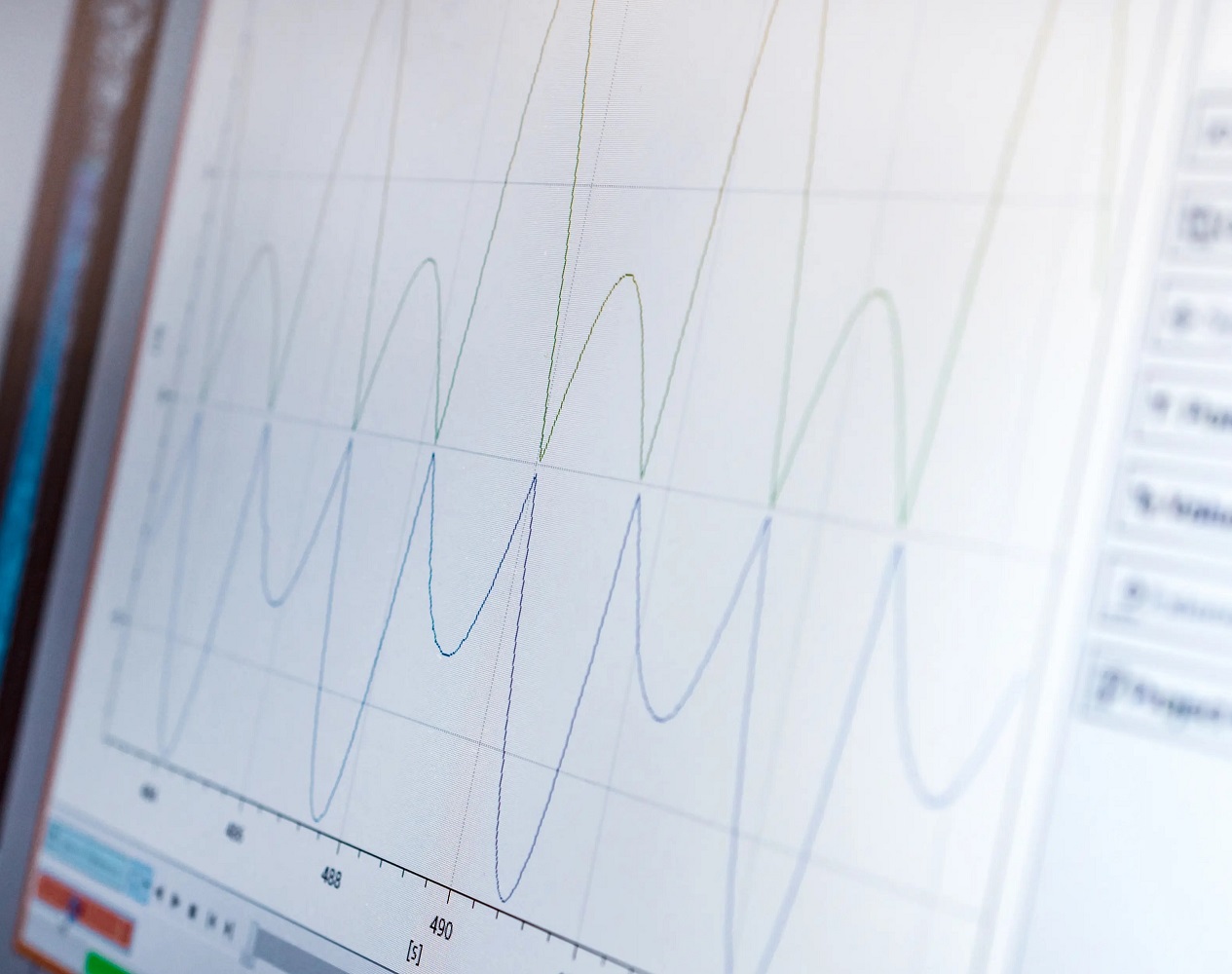

Avec un niveau de tension nettement inférieur (1,8 V contre 3,3 V), un nombre de broches réduit et une fréquence de fonctionnement deux fois plus rapide (66 MHz contre 33 MHz), les progrès techniques de la nouvelle norme eSPI sont énormes. Grâce à ces avantages techniques, l'eSPI devrait remplacer l'interface LPC (Lower Pin Count), qui est utilisée depuis plus de 15 ans sur le marché informatique et qui est considérée comme un standard courant.

Le niveau de signal plus bas réduit la puissance nécessaire. Il supprime également le bruit du signal qui apparaît souvent à des cadences plus élevées. Le nombre réduit de broches diminue le nombre de pistes nécessaires sur le circuit imprimé. eSPI nécessite un maximum de 8 broches pour un esclave : sélection de la puce, horloge, 4 lignes de données, alarme (en option) et réinitialisation.

La fréquence d'horloge accélérée permet une plus grande largeur de bande pour le transfert de données et des opérations plus rapides : 4x 66 MHz.

Pour répondre aux exigences du produit, les développeurs de systèmes peuvent choisir la fréquence d'horloge maximale à soutenir : 20, 25, 33, 50 ou 66 MHz.

Avec la stabilité d'une norme définie à l'échelle de l'industrie, l'eSPI peut soutenir le développement futur des plates-formes client et serveur, y compris les périphériques et la mémoire, pendant de nombreuses années.

solution d'analyse de protocole eSPI

2 550,00 €*

En stock, délai de livraison : 1 à 3 jours