Entrée / sortie de données de gestion (MDIO)

Management Data Input / Output (MDIO) est un bus sériel à 2 fils qui permet de gérer les PHY ou les appareils de la couche physique dans les Media Access Controllers (MAC) dans les appareils Gigabit Ethernet. La gestion de ces PHYs est basée sur l'accès et la modification de leurs différents registres.

MDIO a été défini à l'origine dans la section 22 de IEEE RFC802.3. Dans la spécification originale, une seule interface MDIO peut accéder à jusqu'à 32 registres dans 32 appareils PHY différents. Ces registres fournissent des informations d'état et de contrôle comme : L'état de la connexion, la capacité et la sélection de la vitesse, la désactivation en cas de faible consommation d'énergie, le mode duplex (plein ou moitié), la négociation automatique, la signalisation des erreurs et le bouclage.

Pour répondre aux exigences croissantes des appareils Ethernet 10 gigabits, les ajouts suivants à MDIO ont été fournis dans la section 45 de la spécification 802.3ae :

- Accès à 65 536 registres dans 32 appareils différents sur 32 ports différents

- Code OP et code ST supplémentaires pour l'accès au registre des adresses indirectes pour l'Ethernet 10 gigabits

- Signalisation d'erreur de bout en bout

- Plusieurs points de bouclage

- Spécification électrique basse tension

Fonctionnement théorique

Le bus MDIO a deux signaux : Management Data Clock (MDC) et Managment Data Input / Ouput (MDIO).

MDIO dispose d'une terminologie spécifique pour définir les différents appareils sur le bus. L'appareil qui contrôle le bus MDIO est identifié comme une Station Management Entity (STA). Les appareils cibles qui sont gérés par le MDC sont appelés MDIO Manageable Devices (MMD).

La STA initie toute la communication dans MDIO et est responsable de la commande de l'horloge sur MDC. MDC a une fréquence de jusqu'à 2,5 MHz.

Clause 22

La clause 22 définit le format cadre de base pour la communication MDIO (image Links), qui se compose des éléments suivants.

| ST | 2 bits | Début de la trame (01 pour la clause 22) |

| OP | 2 bits | Code OP |

| PHYADRESS | 5 bits | Adresse PHY |

| REGADRESS | 5 bits | Adresse du registre |

| TA | 2 bits | Temps de rotation pour changer la propriété du bus de STA à MMD si nécessaire |

| DATA | 16 bits | Data Driven by STA during write Driven by MMD during read |

Le format de la trame ne permet qu'un numéro de 5 bits à la fois pour l'adresse PHY et pour l'adresse du registre, ce qui limite le nombre de MMD auxquels la STA peut s'interfacer. De plus, la clause 22 MDIO ne supporte que les appareils tolérants 5 V et ne dispose pas d'une option basse tension.

Clause 45

Pour corriger les défauts de la section 22, la section 45 a été ajoutée à la spécification 802.3. Dans la section 45, la prise en charge des appareils basse tension jusqu'à 1,2 V a été ajoutée et le format du cadre (illustration 14) a été étendu pour permettre l'accès à de nombreux autres appareils et registres. Certains éléments du cadre étendu ressemblent au cadre de données de base :

| ST | 2 bits | Début de la trame (00 pour la clause 45) |

| OP | 2 bits | Code OP |

| PHYADR | 5 bits | Adresse PHY |

| DEVTYPE | 5 bits | Type de dispositif |

| TA | 2 bits | Temps de rotation pour changer la propriété du bus de STA à MMD si nécessaire |

| ADDR/DATA | 16 bits | Address ou Data Driven by STA for address Driven by STA during write Driven by MMD during read Driven by MMD during read-increment-address |

Le changement le plus important dans la section 45 est l'accès aux registres. Dans la section 22, une seule trame indiquait à la fois l'adresse et les données à lire ou à écrire. La clause 45 change ce paradigme. D'abord, une trame d'adresse est envoyée pour indiquer le MMD et le registre. Une deuxième trame est ensuite envoyée pour effectuer la lecture ou l'écriture.

L'ajout de cet accès à deux cycles a l'avantage que la clause 45 est rétrocompatible avec la clause 22, ce qui permet aux appareils d'interagir entre eux. Deuxièmement, en créant un cadre d'adresse, l'espace d'adresse du registre passe de 5 bits à 16 bits, ce qui permet à une STA d'accéder à 65.536 registres différents.

Pour y parvenir, plusieurs modifications ont été apportées à la composition du cadre de données. Un nouveau code ST (00) est défini pour identifier les cadres de données de la clause 45. Les codes OP ont été étendus pour indiquer un cadre d'adresse, un cadre d'écriture, un cadre de lecture ou un cadre d'adresse d'incrément pour la lecture et la relecture. Comme l'adresse de registre n'est plus nécessaire, ce champ est remplacé par DEVTYPE pour indiquer le type d'appareil cible. Le type d'appareil étendu permet à la STA d'accéder à d'autres appareils en plus des PHY.

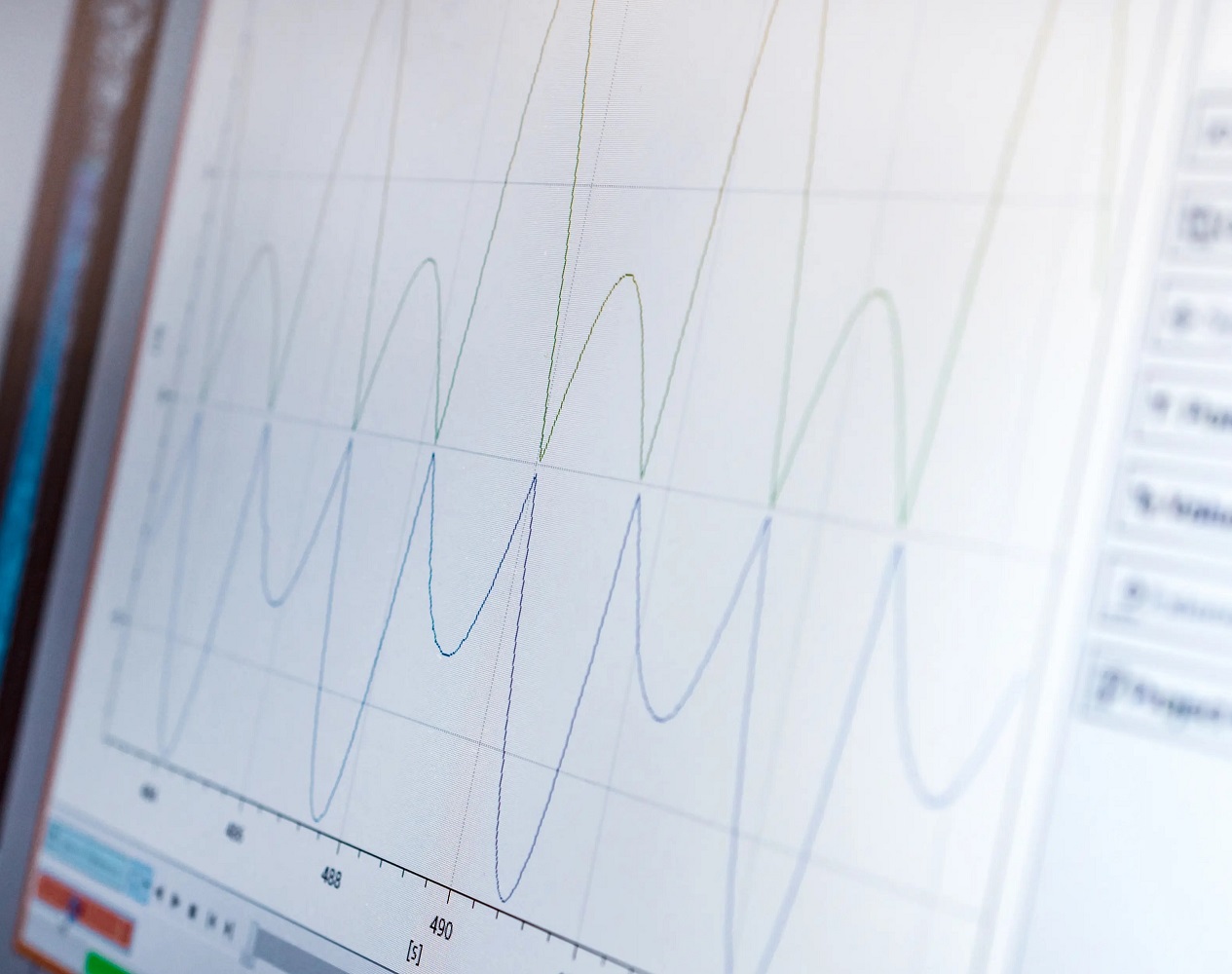

Analyseur de protocole MDIO

Pour déboguer un système, un analyseur de protocole est souvent la meilleure solution pour découvrir et corriger rapidement les erreurs. Pour le protocole MDIO, l'analyseur de protocole Beagle I2C/SPI/MDIO de Total Phase est idéal. Il permet à l'utilisateur de surveiller le bus sans distorsion. Après avoir connecté l'analyseur de protocole MDIO de Beagle au PC via USB, le trafic du bus peut être surveillé et analysé avec le logiciel correspondant (Data Center). L'analyseur de protocole MDIO dispose d'une mémoire interne dans laquelle il enregistre toutes les données entrantes et est le seul analyseur de protocole disponible sur le marché à pouvoir afficher en temps réel